pcb手工制板步骤(PCB设计-Allegro软件入门系列第二十四讲-等长设置)

在高速PCB设计上,我们往往看看PCB上面有蛇形线,这些线是为了信号时序匹配,减少同组信号的相对延迟而绕线,本节开始讲解一下在Allegro 软件下,如何对高速信号网络进行等长设置

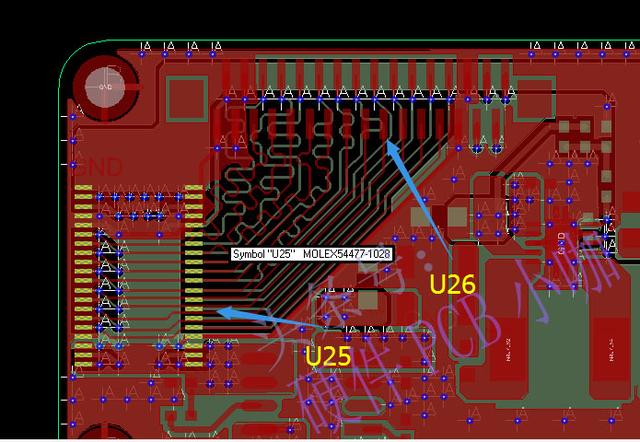

本节以一个CPU跟一个插座的信号组合的PCB为范例,演示等长设置

《一》无串电阻类的等长

(1)如图建立需要等长的管脚对,直到所有需要的网络建立完全

(2)按住Ctrl,选择所有的管脚对,右键选择Create Match Group,这里我改名为MG_SENSOR

(3)点击OK后,就会在电气规则的这里产生这个Match Group

(4)设置等长误差,这里我填写0:30MIL,具体情况要看信号的速率决定,我这个传感器速度不高,30mil已经很不错了。

(5)在改Match Group上右键Analyze

(6)设置Target

(6)点击分析如图,就可以看到哪些不满足要求的网络了,绿色是满足的网络,而红色是不满足的,所以我们要对红色的网络进行绕线即可,直到所有Match Group的网络都是绿色。

下一节:讲解等长查看进度等长技巧

有兴趣学allegro的同学或者朋友,谢谢大家的阅读!

原创文章,技术分享!

有问题的不懂的可以留言大家讨论,谢谢大家支持!

,

免责声明:本文仅代表文章作者的个人观点,与本站无关。其原创性、真实性以及文中陈述文字和内容未经本站证实,对本文以及其中全部或者部分内容文字的真实性、完整性和原创性本站不作任何保证或承诺,请读者仅作参考,并自行核实相关内容。文章投诉邮箱:anhduc.ph@yahoo.com