计算机逻辑算术运算规则(算术逻辑运算部件的功能设计与线路实现)

算术与逻辑运算线路是计算机运算器的核心部件,从功能的角度看,它要完成对数值数据的算术运算功能,给出运算结果的数值和结果的特征信息(例如结果的符号、向更高位的进位、结果是否为0和结果是否溢出),还要完成对逻辑数据的逻辑运算功能。

算术逻辑运算部件的核心就是加法器。设计实现一位加法器的过程是:

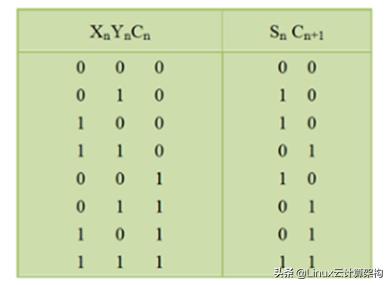

(1)写出加法器的真值表;

(2)用布尔代数写出逻辑表达式;

(3)对得到的逻辑表达式进行适当地化简,就可找出所用电路及其连接关系。每一位加法器实现对2个二进制数(Xi、Yi)和一个进位输入(Cn)的加法运算,产生一位的相加之和(Sn),以及一位的进位输出C(n 1),图3.1中给出了这一设计结果。

值真表表征逻辑事件输入和输出之间全部可能状态的表格。列出命题公式真假值的表。通常以1表示真,0 表示假。命题公式的取值由组成命题公式的命题变元的取值和命题联结词决定,命题联结词的真值表给出了真假值的算法。

真值表是在逻辑中使用的一类数学表,用来确定一个表达式是否为真或有效。 (表达式可以是论证;就是说,表达式的合取,它的每个结合项(conjunct)都是最后要做的结论的一个前提。)

真值表被用来计算真值泛函表达式的值(就是说是一个判定过程)。真值泛函表达式要么是原子(就是说是命题变量(或占位符)或命题函数 - 比如 Px)或建造自使用逻辑运算符(就是说 ∧ (AND),∨ (OR),¬ (NOT) - 例如 Fx & Gx)的原子公式。

真值表中的列标题展示了 (i) 命题函数与/或变量,和 (ii) 建造自这些命题函数或变量和运算符的真值泛函表达式。行展示对 (i) 和 (ii) 的 T 或 F 指派的每个可能的求值。换句话说,每行都是对 (i) 和 (ii) 的不同解释。

加法器的真值表、逻辑表达式,线路图

如果把Sn=Xn and Yn,Sn=Xn or Yn的逻辑运算功能也添加进去,需要用一个与门实现与运算,用一个或门实现或运算,再将其与加法电路归并到一起,就得到可完成算术和逻辑运算功能的ALU

ALU的原理性组成框图

时要使用一个多路选择器电路,通过2位的功能选择信号(例如信号为00输出加法运算的和,为10输出“与运算”的结果,为11输出“或运算”结果),从三个运算结果中选择其一作为输出。进位信号与逻辑运算无关,只用于加法运算。

计算机系统中,减法运算是用加法器电路实现的,此时需要把减数每一位取反后送ALU的数据输入端,并向ALU最低位提供进位信号1。为此需要依据是加运算还是减运算,选择把Yn的值或者Yn每一位取反的值送ALU,通常用多路选择器电路实现。

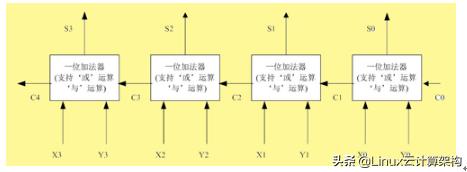

可以用多个一位的ALU组成多位的ALU部件。

位的加法器框图

给出一个4位的ALU框图。4位之间要建立正确的进位连接,低一位的进位输出送到相邻高位作为输入。

在多位的ALU线路中,加法运算进位信号的传送方式是影响加法器运算速度的主要因素。

如果加法运算的进位信号选用如上图所示的串行方式传送,即每一级都要等待前一级进位信号的传送,所用的时间比较长,会影响系统性能。解决的办法是选用超前(并行)进位的方式处理进位信号,实现思路是:高位加法器不是简单地等待进位信号从最低位逐位传送过来,而是争取每位加法器几乎可以同时得到自己的进位输入信号,从而实现并行传送进位输入信号。

,免责声明:本文仅代表文章作者的个人观点,与本站无关。其原创性、真实性以及文中陈述文字和内容未经本站证实,对本文以及其中全部或者部分内容文字的真实性、完整性和原创性本站不作任何保证或承诺,请读者仅作参考,并自行核实相关内容。文章投诉邮箱:anhduc.ph@yahoo.com