全志c100芯片(全志A40i开发板硬件说明书)

本文档主要介绍全志A40i开发板丰富的硬件接口资源,以及开发设计中的一些注意事项等内容。全志这块A40i的开发板,是源自创龙科技最新代表作品,其核心板采用“100%国产+工业级”设计,外观精美,可玩性很高,在国产芯片势头正猛的情况下,究竟真的是电力用户的首选吗?一起来看看!

由于内容篇幅过长,故分为上中下三篇文章,本篇章为中,内容详细覆盖了:Watchdog接口、CAMERA接口、AUDIO接口、MIPI显示接口、RGB显示接口、LVDS显示接口、HDMI OUT接口、VGA显示接口、CVBS OUT接口、TVIN接口等,欢迎各位嵌入式爱好者关注查看。

创龙科技TLA40i-EVM是一款基于全志科技A40i处理器设计的4核ARM Cortex-A7高性能低功耗国产开发板。

开发板硬件资源图解1

开发板硬件资源图解

A40i处理器的IO电平标准一般为1.8V和3.3V,上拉电源一般不超过3.3V,当外接信号电平与IO电平不匹配时,中间需增加电平转换芯片或信号隔离芯片。按键或接口需考虑ESD设计,ESD器件选型时需注意结电容是否偏大,否则可能会影响到信号通信。

设计注意事项:

TWI0总线在核心板内部已设计上拉2K电阻至3.3V。

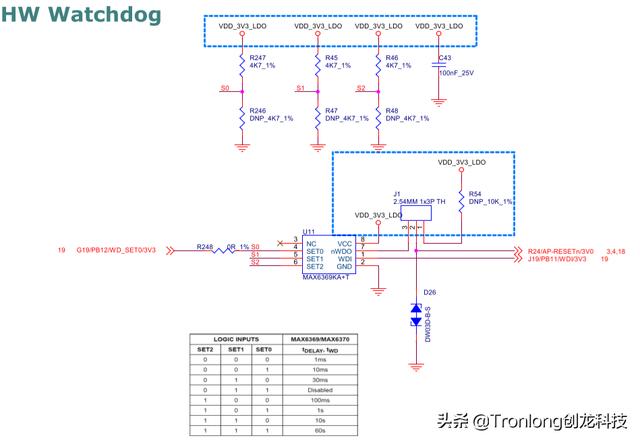

Watchdog接口评估底板引出3pin 2.54mm间距排针(J1)作为Watchdog功能配置接口,可通过跳线帽配置使能Watchdog功能。软件上可通过G19/PB12/WD_SET0来控制Watchdog超时时长。

图 44

图 45

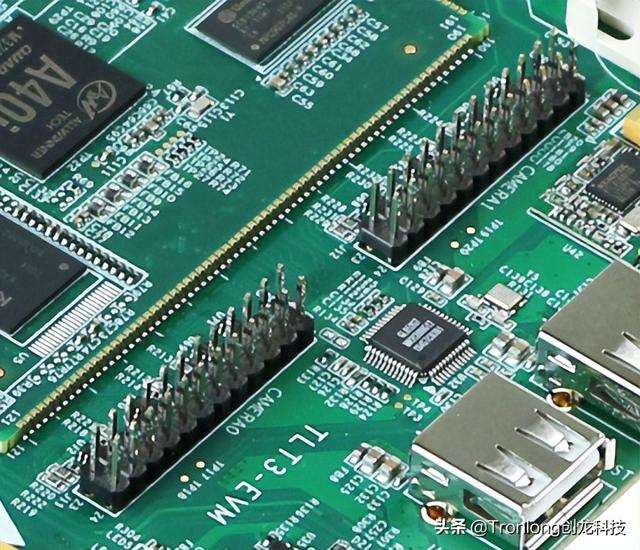

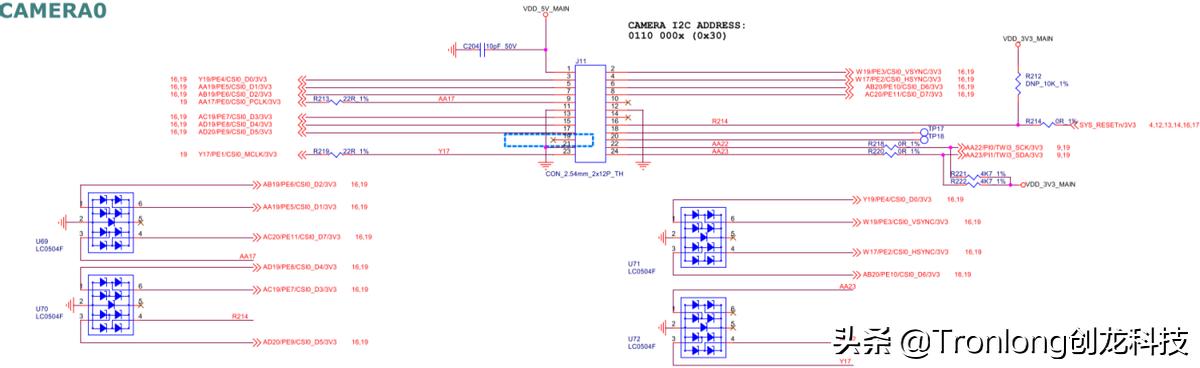

CAMERA接口J11为CAMERA0摄像头接口,J12为CAMERA1摄像头接口,均采用2x 12pin排针方式,间距2.54mm。

图 46

图 47

图 48

AUDIO接口CON15为LINE IN音频接口,CON26为H/P(Headphone) OUT音频接口,均采用3.5mm音频插座。

图 49

图 50

CON28为MIPI显示屏接口,采用40pin FFC连接器,间距0.5mm。

J7为MIPI显示屏的电容触摸接口,采用6pin FFC连接器,间距0.5mm。

图 51

图 52

设计注意事项:

(1)若J7的nINT引脚需分配使用其他IO,请使用引脚信号名称包含EINTx字段(支持中断功能)的IO引脚。

RGB显示接口CON11为RGB显示屏接口,采用40pin FFC连接器,间距0.5mm。

图 53

图 54

设计注意事项:

RGB显示接口使用的LCD0信号与LVDS0、LVDS1信号为复用关系,如下图所示。

图 55

通过F24/PB20/PWM4引脚输出PWM控制LCD背光,外部预留下拉4.7K电阻到地。

RGB显示接口、LVDS显示接口同时连接了TPX1、TPX2、TPY1、TPY2四线电阻触摸信号,请勿同时连接两种显示设备。

LVDS显示接口CON12为双路8bit LVDS显示接口,采用2x 15pin双排针,间距2.0mm,包含LVDS信号及供电电源。CON13为背光控制接口,采用6pin白色端子座,间距2.54mm。J5为电阻触摸屏接口,采用4pin排针,间距2.54mm。

图 56

图 57

设计注意事项:

LVDS0、LVDS1信号与LCD0信号为复用关系。

LVDS显示接口、RGB显示接口同时连接了TPX1、TPX2、TPY1、TPY2四线电阻触摸信号,请勿同时连接两种显示设备。

HDMI OUT接口CON10为HDMI OUT视频输出接口,采用标准19pin HDMI座。

图 58

图 59

设计注意事项:

HDMI座子的HPLG信号需下拉27K电阻到地,当外部设备接入时,会将此信号拉高。

V9/HDMI_HSCL和W9/HDMI_HSDA的IO电平为3.3V,需转换为5V电平再引出至HDMI座。

VGA显示接口CON14为VGA视频输出接口,由TVOUT0、TVOUT1、TVOUT2引出,采用15pin VGA座。

图 60

图 61

设计注意事项:

(1)U5/PD26/LCD0_HSYNC和U6/PD27/LCD0_VSYNC的IO电平为3.3V,需转换为5V电平再引出至VGA座。

CVBS OUT接口J9为CVBS OUT接口,由TVOUT3引出,采用RCA莲花座。

图 62

图 63

TVIN接口J8为TVIN接口,由TVIN0、TVIN1、TVIN2、TVIN3引出,采用用6pin 2.54mm白色端子形式。

图 64

图 65

本篇第二部分章节已完,第三篇内容将讲解关于A40i开发板的USB接口、Ethernet接口、4G模块拓展接口、WIFI模块、蓝牙模块、SATA接口、SDIO接口、拓展IO信号接口等。通过详细的A40i开发板硬件资源介绍,相信大家对于这块国产板卡还是非常感兴趣的,应用在智能电力领域上也非常合适,关于显示相关的多个特色案例也非常丰富,可以了解。

,免责声明:本文仅代表文章作者的个人观点,与本站无关。其原创性、真实性以及文中陈述文字和内容未经本站证实,对本文以及其中全部或者部分内容文字的真实性、完整性和原创性本站不作任何保证或承诺,请读者仅作参考,并自行核实相关内容。文章投诉邮箱:anhduc.ph@yahoo.com