芯片制程到瓶颈后还有什么进化(人类陷入制程焦虑)

知名芯片调研公司IC Insights曾做过一个有趣的估算,如果想追赶上全球最大的晶圆代工厂台积电,起码需要五年时间外加一万亿人民币。这里追赶的对象,指的就是台积电在芯片先进制程上的制造能力。

芯片先进制程的魔力不需赘述,在技术上它是手机、平板、电脑等消费电子产品赖以运转的关键;在经济价值上,掌握先进制程能力的台积电2020年创造了1197.87亿元人民币的净利润;在战略重要性层面,芯片已关系到产业安全乃至地缘之间的经贸关系……

但有意思的是,事实上,并非所有芯片工厂都在拼命追求制程。全球前五的晶圆代工厂——台积电、三星、联电、格罗方德、中芯国际中,中芯国际在制程工艺上不停追赶,然而排名三四号位的联电、格罗方德都已几乎放弃了先进制程的研究。

联电在2018年时已放弃对12nm制程的研发,当时还是全球第二大芯片代工厂的格罗方德也随后宣布放弃7nmFinFET工艺的研发。如今,纵观全球的晶圆代工厂(Foundry)和IDM模式(Integrated Device Manufacture),实际有能力生产7nm及更小芯片制程的只有台积电、三星以及稍后一步的英特尔(7nm已taped-in)。

为何各大芯片厂商纷纷放弃对先进制程的研制呢?制程更小的芯片性能就一定更好吗?这其中其实有不少门道。

芯片的先进制程,简单来说就是把芯片从大做小,具体是指芯片晶体管栅极宽度的大小,数字越小对应晶体管密度越大, 芯片功耗越低,性能越高,但要实际做到这一点却并不容易。从芯片的进化历史来看,芯片的研发主要遵循着摩尔定律,即每18个月到两年间,芯片的性能会翻一倍,使一块芯片内装上尽可能多的晶体管来提升芯片性能。

上个世纪80年代,芯片内晶体管的大小进入微米级,再到2004年,芯片内的晶体管已微缩至纳米级别。此时,问题陆续出现了,纳米级别的晶体管的集成度和精细化程度非常高,要知道一个原子就有0.1nm,在人类物理认知极限上的工艺难度可想而知。

如今出现的最具代表的两个问题是短沟道效应和量子隧穿难题。短沟道效应(short-channel effects)是指“当金属氧化物半导体场效应管的导电沟道长度降低到十几纳米、甚至几纳米量级时,晶体管出现的一些效应”。这些效应主要包括“阈值电压随着沟道长度降低而降低、漏致势垒降低(Drain-induced barrier lowering)、载流子表面散射、速度饱和(Saturation velocity)、离子化和热电子效应”。

被这些复杂的技术术语绕懵了吧,其实简单来说就是,因为晶体管是一个有三个端口的管子——电子从源端跑到漏端,借此完成信息的传递,而决定“跑”的节奏的是其中的一个“开关”,也就是栅端。它的开关由端口对应的电压变化来决定。

而由于大部分时候电子的速度都是全速运转,因此传递信息需要的时间也就是芯片一定意义上的效率就由管道长短决定。但是,当管道变得很短后,由于尺寸变小,长沟道时本可以忽略的电场干扰就变多,导致栅端可能“关不严”,也就是所谓的短沟道效应。

短沟道效应对纳米级芯片造成的影响就是,因为管子管不住电,所以只要一通电,芯片内的晶体管就会不停漏电,导致芯片发热和功耗严重,进而影响使用寿命。

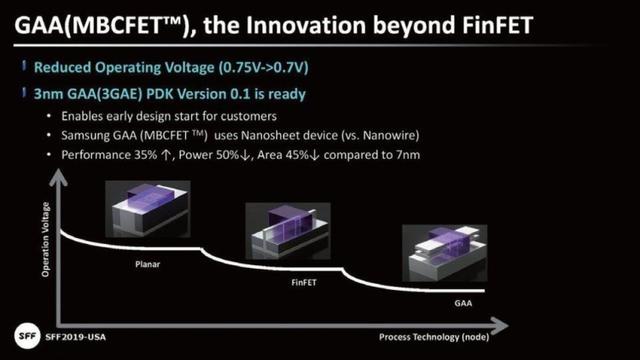

直到1999年胡正明教授发明了鳍式场效应晶体管(Fin Field-Effect Transistor,简称FinFET)—— FinFET可以理解为加强栅对沟道的控制能力,从而减小短沟道效应。由此才在一定程度上延缓了这个问题的办法,如今台积电、三星能做到5nm/7nm都依赖此项技术。

但是到了3nm阶段,FinFET的三面栅的控制作用减弱,短沟道效应再次凸显。直到下一世代的晶体管结构即所谓Gate-All-Around环绕式栅极技术(简称为GAA结构)出现,问题才得以缓解。它可以简单理解为沟道被栅极四面包裹,从而降低操作电压、减少漏电,降低芯片运算功耗与操作温度,从而继续为摩尔定律续命。如今三星的3nm和台积电的2nm都已采用该技术进行研发。

然而,当制程继续往下走时,又一个难题出现在眼前——量子隧穿效应带来的漏电流。该原理已涉及到量子力学相关理论,可以简单理解为当材料逼近1nm的物理极限时,有一定的电子可以跨过势垒,从而漏电。这个问题对于人类来说暂时是无解的,因为物理理论还没有搞清楚这个现象。

可以说不管是FinFET结构还是GAA结构,都是人类通过工艺手段来逼近自己的理论极限,但实现这些结构对芯片产业来说是一件无比困难的事情,不仅技术难度陡然剧增,工艺成本也让一般的芯片企业望洋兴叹。

据SEMI国际半导体产业协会的芯片主流设计成本模型图,采用FinFET工艺的5nm芯片设计成本已是28nm工艺设计成本的近8倍,更复杂的GAA结构耗费的设计成本只会更多,这仅仅只是芯片设计、制造、封装、测试中的设计环节,晶圆代工厂实际研发技术、建厂、买生产设备耗费的资金会更多,如今年三星在美国得克萨斯州计划新建的5nm晶圆厂预计投资170亿美金。

对台积电和三星来说投资数百亿美金来建造一座先进制程的晶圆厂是可以承受的,因为它们已有稳定的客户订单和巨大芯片销量来分担成本,但对于制程相对落后者来说,这是难以承受的。

从成本上它们技术不成熟,还需要花更多的时间、资金成本来突破新技术;芯片质量上来说,即便强如三星在生产采用5nm芯片的高通骁龙888时,也遭外界诟病功耗“翻车”、发热严重等问题,后来者更难在开始阶段就保证芯片的良品率和性能;从客户上来说,采用价格更高的先进制程的客户有限,近来手机、平板、PC等消费电子已增长趋缓,在存量市场下新入局者如非价格和性能上更优,没有机会能争夺过三星和台积电的客户,况且这些老牌霸主先进制程的研发成本已被巨额销量所稀释,成本只会更低。

况且,现今全球的缺芯潮缺的更多是成熟制程的芯片。以汽车行业为例,目前紧缺的为MCU芯片(Microcontroller Unit,微控制器),汽车的ESP车身电子稳定系统和ECU电子控制单元等都需要用到这种芯片,它主要由8英寸晶圆生产,芯片的制程普遍在45-130nm之间。

28nm及以上的芯片工艺都可以叫做成熟制程,整个业界技术非常成熟了,厂家对芯片的成本控制也不会相差太多,三星、台积电在该领域对联电、中芯国际来说没有什么绝对优势。如今,成熟制程芯片极缺,只要有晶圆代工厂有产能就不愁销售不出去,完全不会遇到先进制程中的种种问题,对格罗方德和联电来说,现在投资先进制程可以说是吃力不讨好的事情,两家厂商最近纷纷扩产的也都是成熟制程晶圆厂。

在更广阔的领域,如工业以及军事领域,先进制程芯片反而没有成熟制程芯片可靠。先进制程可以理解为同样功耗、尺寸下可以获得更好的性能,但在工业以及军事领域,对芯片的功耗、发热和占用面积上并没有手机、平板那么苛刻,它们更关注的是芯片在各类极端环境下的可靠性和耐久度。

如,民用芯片、工业芯片和军用芯片所要求的正常工作的温度范围就有很大不同。民用级要求0℃~70℃、工业级要求-40℃~85℃、军用级要求-55℃~125℃,这仅仅是温度这一项指标,工业、军用级芯片还有抗干扰、抗冲击乃至航空航天级别的抗辐射等等要求,这些反而是更精密、更细小的先进制程芯片所难以达到的。

先进制程虽好,但实现难度既艰难适用范围也有其局限性。虽然今天芯片已经成了老百姓都在关心的话题,而且人们天天讨论的往往都是谁达到了几纳米,谁停留在几纳米,但对于一个复杂而庞大的芯片产业来说,制程并不是衡量芯片价值的唯一标准。

,免责声明:本文仅代表文章作者的个人观点,与本站无关。其原创性、真实性以及文中陈述文字和内容未经本站证实,对本文以及其中全部或者部分内容文字的真实性、完整性和原创性本站不作任何保证或承诺,请读者仅作参考,并自行核实相关内容。文章投诉邮箱:anhduc.ph@yahoo.com