pcie功能测试关注的是设备核心么(你未来的坐骑就是移动的数据中心)

汽车的“信息化、智能化”为汽车行业带来了新的概念,软件定义汽车。它代表着车内软件的数量和价值(包括电子硬件)超过了机械硬件,代表着汽车行业的逐步转型,从高度的电子机械终端到智能、可扩展的移动电子终端并可持续升级。要成为如此智能的终端,汽车必须预先嵌入高级的硬件,而硬件的功能和价值通过整个生命周期中的OTA逐渐激活及增强。行业的价值链将从一站式的硬件销售变成持续的软件和服务优化,而消费者也期望汽车有类似智能手机的行为的客户感受。 因此汽车的电子电气架构 (EEA) 需要从传统的分布式模型向中心化、简介化、可扩展化演进。概括的说, EEA 的演进将通过集成、域中心化及车中心化三步演进,如下图所示:

图 1. 汽车电子电气架构演进路线

当前车内的电子电气架构以功能型的域集中形式为主,比如将动力域、底盘域、车身域整合为“车控域”; “智能座舱域”将取代原有的信息娱乐域,实现人机交互和T-box集成功能;“自动驾驶域”将负责高级自动驾驶的感知、规划和决策。当然造车的新势力会更进一步的采用域中心化及车中心化的先进架构实现更高级别的自动驾驶能力,实现“跨域融合”。 智能座舱作为与消费者最直接的接触空间,是客户交 互体验差异化的关键,汽车行业中的热点并且不断的加速演进。这也带来了智能座舱在数字仪表、信息娱乐等多个显示域实现 HMI 的无缝连接,并且屏幕的尺寸也越来越大,多模交互、中控多屏以及智能联屏是智能座舱发展的趋势。

如下图所示,参考华为海思的智能座舱框图,典型的座舱域控制其中可能包含了各种各样的显示高速总线,比如GMSL/FPD-LINK/MIPI DSI/CSI 等连接多种屏幕,同时也包含了各种车内互联接口,比如 CAN/ CAN-FD/USB2.0/100BASE-T1 等用于与座舱中各种传感器、音频设备等外设的互联,从而可以通过硬件架构的集中和统一的智能化处理带来更丰富的沉浸式用户体验。

图 2. 智能座舱示意图参考海思

作为设计者要面对下一代高速的视频及外设接口信号完整性,冗余的硬件设计满足消费者的全生命周期迭代升级要求,轻量化及降低线束,以及更低的功耗等等各种挑战。

图 3. 不断推进的分辨率及 SERDES 高速接口

自动驾驶域涉及到感知、决策和执行三个层面,随着汽车智能化水平的不断提高,驱使着自动驾驶算力的不断增加以及融合感知能力的不断增强。这都使得传感器接口数量和带宽都高速增长,涉及到 MIPI DPHY/ CPHY/SERDES/车载以太网等等高速互联接口;以及内部计算接口总线、存储总线、芯片互联总线诸如 PCIe Gen3/4、LPDDR4/5、XFI 等等。这都为硬件工程师带来不断提升的高速信号完整性及电源完整性设计与测试的挑战。

以下将会对新一代电子电气架构下,智能座舱域及自 动驾驶域内部涉及到的各类高速总线信号完整性及电源完整性测试进行分析和总结,帮助汽车行业工程师们能够应对日益提升的汽车硬件设计域测试要求。

图 4. 自动驾驶域示意图

图 5. 参考 nVidia Orin 计算平台示例

PCIe Gen 2/3/4 测试

PCIe是数据中心和客户端应用中使用的主要新兴高性能存储和串行总线,实现了外设之间的数据通信。下图为PCIe 总线传统的典型应用:由于汽车向“信息化、智能化”不断演进,汽车也越来越像移动的数据中心,承载着大量的计算场景,从而PCIe的大量使用也是必不可少,并且速率也在随着芯片算力、消费接口升级而不断提高。

图 6. PCIe 典型应用场景

图 7. PCIe 链路层级示意及链路实现方案

与任何串行数据标准一样, PCI Express 可以视作“由多个层组成的堆栈”,堆栈中包括通过传输介质传送电子信号的物理层;把信号解释为有意义的数据的逻 辑层;传输层等等。每个层有相应的标准和一致性测 试程序。而其中PHY 层(物理层)涵盖了两个子层:逻辑层和电气层。PHY的物理部分处理高速串行分组交换和电源管理机制。PHY 的逻辑层处理复位、初始化、编码和解码。电气子模块和逻辑子模块还可能包 括特定标准功能。

PCI Express 链路由称为通路的双单工传输方案集合组成。每条通路有一个发送和接收差分对,每条通路共有四根走线(以图中的 PCIe x4 链路为例)。 PCIe 标准由PCI-sig组织负责维护,从机械接口来 看有 CEM 等形式,并具备一致性测试要求;而对于芯片到芯片的连接,则有 PCIe 的 Base 规范来进行规定,但是没有一致性要求。其主要的信号特点:

1. 采用AC耦合的差分信令传输

2. 应用100MHz的参考时钟,既可以是公共时钟也可以是分离时钟

3. 总线宽度可扩展,包含x1、x2、x4、x8、x16通路数目

4. 可扩展传输速率,包含2.5GT/s (Gen1)、5GT/s (Gen2)、8GT/s (Gen3)、16GT/s(Gen4) 等等

5. 多种连接方式,如CEM、U.2、M.2 及 PCB直连等

图 8. PCIe 标准分类

如下图所示,典型的整条高速串行链路由发射机、信道及接收机三部分组成。对于芯片到芯片的PCIe链路,通常标准会定义在发射机引脚进行测试,并满足PCIe Base的规范要求。 由于PCIe芯片中还包含了发射机及接收机均衡以抵抗信道的衰减;所以调试时往往还需要嵌入信道的模型,并模拟PCIe芯片的接收机均衡来评估芯片内部进行均衡后的信号质量。而这些往往都可以在示波器的软件中进行模拟。

图 9. PCIe 典型链路测试示意

PCIe 链路性能列在下面以供参考:

在实际应用中,PCIe 速率是向下兼容,比如 Gen4 的发射机也会兼容 Gen1、2、3 的所有速率和均衡方式,并且通过协商的方式决定最终的链路工作模式;假如我们需要进行所有发射机和接收机均衡的调试和评估,需要非常纷繁复杂的测试手段。

泰克 PCIe 测试解决方案

泰克PCIe测试解决方案不仅仅针对PCIe一致性测试,而且也支持PCIe Base测试所需要的测量项目,并且具备优异的三模测试探头、功能完备的串行数据链路分析软件(SDLA)及协议解码功能,可以让我们在PCIe的调试、测试和评估中得心应手。

泰克的 SDLA 串行链路分析软件支持针对发射机、接收机均衡模拟,以及信道的嵌入与去嵌,因而在进行复杂的PCIe链路的模拟中通过一次测试模拟出不同均衡下,针对不同信道模型各个节点的波形进行分析比对。并且 SDLA 支持丰富的信道模型嵌入和去嵌,最大程度提高测试的便利性,比如单端或差分S参数,示波器及探头模型、传输线模型、RLC 模型、传递函数等等:

图 10. 泰克 SDLA 串行链路分析软件

图 11. SDLA 支持丰富的信道模型类型

接收机均衡除了支持自定义CTLE、FFE/DFE均衡设 定外,同时也支持IBIS-AMI模型,真实模拟芯片的均衡能力。

图 12. SDLA 支持 IBIS-AMI 模型

接收机均衡除了支持自定义 CTLE、FFE/DFE 均衡设 定外,同时也支持 IBIS-AMI 模型,真实模拟芯片的均衡能力: 此外,泰克还提供了SignalConnectTM 信道测量建模 功能,方便直接对信道进行测量和生成模型,并方便快捷的导入至SDLA中进行链路分析:

图 13. 泰克 SignalCorrect 信道测试建模功能

在调试与评估中,泰克还提供了SR-PCIe协议解码功能,帮助发现并定位通信链路中可能存在的问题:

图 14. 泰克PCIe协议解码功能,并能实现点击任意符号波形自动跳转到对应位置功能

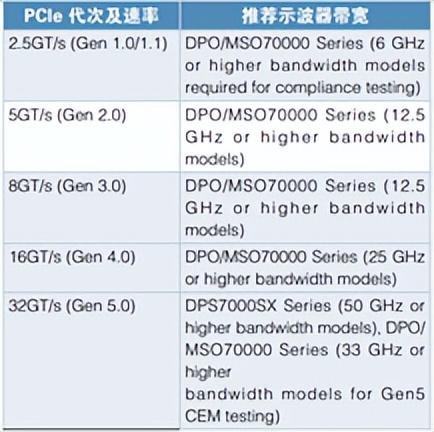

推荐的示波器的选择如下表:

总体来说,泰克PCIe 解决方案提供完备的软件支持PCIe Base及CEM一致性测试,提供丰富的调试工具如SDLA、SignalCorrect、协议解码等,使得PCIE在芯片到芯片互联的测试与评估更加简单快捷,让产品可以更快投放到市场,从而获得竞争优势。

,

免责声明:本文仅代表文章作者的个人观点,与本站无关。其原创性、真实性以及文中陈述文字和内容未经本站证实,对本文以及其中全部或者部分内容文字的真实性、完整性和原创性本站不作任何保证或承诺,请读者仅作参考,并自行核实相关内容。文章投诉邮箱:anhduc.ph@yahoo.com