arm 服务器芯片(的服务器芯片路线图)

Arm服务器芯片有三波浪潮。第一波浪潮是Calxeda、Applied Micro、AMD、Marvell、Nvidia和三星等公司的使用浪潮,但目前来看并不理想。第二波浪潮是Broadcom、Cavium、高通和Nuvia等公司。

现在,第三波Arm服务器芯片浪潮开始出现,由亚马逊、微软、谷歌、阿里巴巴和腾讯,以及一些独立的芯片设计企业(主要是安培计算、海思、英伟达和 SiPearl)领导,与Arm公司合作,这样来看Arm服务器芯片是将长期存在的。

Arm服务器芯片引起第三次浪潮的魅力在于2018 年 10 月 Arm 将其客户芯片设计与其服务器芯片设计分开。在Neoverse的努力下,Arm内核从一开始就被设计为具有服务器工作负载(以及它们所需的更高晶体管)所必需的功能,以及L2缓存和网状互连等将它们捆绑在一起的核心复合体。

Neoverse 参考架构允许芯片设计人员插入他们选择的 DDR 内存、PCI-Express 外围设备和网络接口控制器,在很大程度上降低了创建服务器芯片设计的风险,同时允许灵活性,对于那些拥有Arm 架构许可证的人来说,是否为Neoverse内核的衍生产品,都能够制作定制的Arm内核。

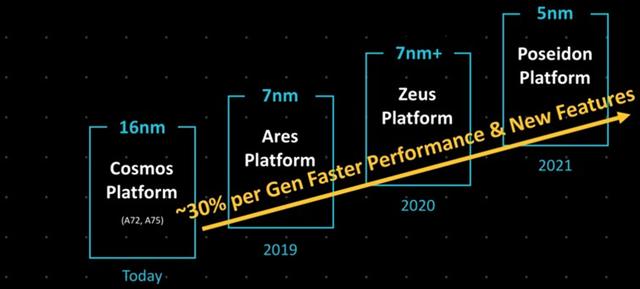

当时Neoverse参考平台的承诺是每年开发一个新的Arm服务器平台,并在每一代中提供30%或更多的性能。

这是一个简化的路线图,旨在创建基于 Arm 架构的 CPU,其内核带宽从 4 到 128 个,每秒内存带宽从千兆字节到兆字节,以满足从边缘到云数据中心的计算需求。

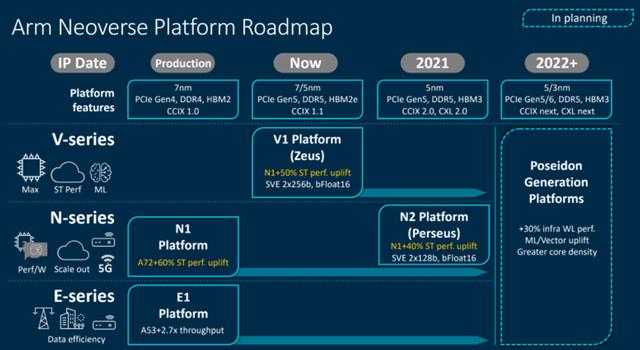

2020年9月,随着V系列(强调浮点计算的fat向量)、N系列(具有高吞吐量整数性能)和E系列(旨在为适度计算需求提供能效)的创建,Neoverse路线图得到了更全面的扩展和充实。

2021 年 4 月,Arm公司披露了其服务器 CPU 设计的三个不同系列的一些细节。

V系列内核是2019年末或2020年初左右的想法,受到超大规模和和云建设者的推动,使得V系列内核在Arm许可的内核中具有更高的性能,包括整数和浮点。

随着高端 V 系列和低端 E 系列的加入,Arm 无法达到其Neoverse 设计的年度节奏目标,预计 2021 年的“波塞冬”系列芯片的推出延迟至2023 年及以后。市场还没有为这种节奏做好准备。Neoverse N1 内核必须由少数芯片设计人员建立并以合理的数量用于生产,然后市场才能完全相信 Neoverse 的可以生产出商业芯片。

这就是为什么 Arm可以用更多的核心变体来充实 Neoverse 路线图,并让每个人都知道它有后续的工作。

更新的 Neoverse 路线图

添加的新内核是“Demeter”V2 内核,它是 Nvidia 选择在其“Grace”Arm 服务器 CPU 中使用的内核,预计将于明年开始发货。Nvidia 对它在 Grace 中使用的内核保持谨慎态度,使得许多人怀疑它这次创建了自己的内核,就像它在2011年1月推出的“Denver”Arm 服务器 CPU 一样,该芯片是英伟达未来的产品线,但由于一系列复杂的原因没有交付。

这并不是说 Nvidia 不会使用其 Arm 架构在其未来的 Arm CPU 中创建定制内核。Ampere Computing开始使用 N1 内核,并正在为未来的芯片开发自己的内核,而 AWS开始使用带有 Gravton1 的半定制“Maya”Cortex-A72 内核,转向使用 Graviton2 的 N1 内核,并在其新的 Graviton3 中使用 V1 内核。

Arm基础设施产品解决方案副总裁DermotO'Driscoll告诉The Next Platform:“Arm 生态系统的美妙之处在于我们提供的灵活性,有些合作伙伴认为,他们希望将这种灵活性提升到设计自己核心的水平。这为这些合作伙伴和我们提供了一系列不同的产品。我们显然坚信Neoverse是市场上最好的。但我们也相信,我们的合作伙伴将为市场带来真正引人注目和有趣的解决方案。”

无论如何,“Poseidon”不再是一个产品系列,而是开始看起来是未来 V3 核心和围绕它的平台的名称。

这是一个更完整的路线图,展示了三代 V、N 和 E 内核设计

可以看到每个 Arm 内核系列的级别,即一个相干网状网络 (CMN),它将内核彼此链接,并链接到 CPU 上的 L2 缓存和其他控制器和接口。

Demeter V2 内核、 DDR5 内存和PCI-Express 5.0 外围控制器配对,并将支持用于加速器的 CXL 2.0 相干内存协议,这也允许跨服务器进行内存池。V2 内核支持 Armv9-A 架构,该架构支持第二代可扩展向量扩展 (SVE2) 向量数学设计,该设计具有四个 128 位向量捆绑在一起,支持 INT8 和 BF16 格式以及通常的单精度 FP32 和双精度 FP64 浮点数学运算。

V2 内核具有 64 位虚拟内存寻址和 48 位物理寻址,这意味着单个插槽中的这些内核的复合体可以连接多达 256 TB 的物理内存。对于传统的 CPU 用例来说,这似乎已经足够了。但是对于像 IBM 这样支持 Power10 芯片的非常大的共享内存池,IBM 添加了足够的位来支持每台服务器 2 PB 的物理内存。

V2 内核将具有 64 KB 指令 L1 缓存、64 KB 具有纠错功能的 L1 数据缓存(最后一位是新的),以及将 L2 缓存从 V1 内核设计的 1 MB 提升到 2 MB 的选项。Arm在没有具体说明的情况下承诺“市场领先的整数性能”,但Grace的SPEC整数速率性能指标,在SPECintU rate_2017吞吐量测试中,它们在72个活动内核中的性能相当好,估计为370。

将与V2核心一起使用的CMN网格可以跨越256个核心,因此可以跨越512 MB的二级缓存。这是 V1 内核的 2 倍内核和 4 倍 L2 内存,考虑到 CMN 网格具有 4 TB/秒的总带宽,这是合理的。V2 平台支持 DDR5 和低功耗DDR5 (LPDDR5) 主内存,后者被 Nvidia 用作Grace CPU 中的主内存。V2 平台支持PCI-Express 5.0 外设,可以运行 CXL 2.0 内存池协议,但必须等到 PCI-Express 6.0 和 CXL 3.0 协议才能通过 PCI-Express 切换链接到 CPU 之间共享内存。

预计将于明年由 Arm发布的Poseidon V-Next 核心设计可能会发生这种情况。目前正在开发,它支持 DDR5 内存、PCI-Express 6.0 外设和 CXL 3.0 协议。

Perseus N2 内核遵守 ARMv9-A 规范。使用N2 核的 CPU 主要针对 12 核到 36 核、功率在 30 瓦到 80 瓦之间的机器。V1 核心在超大规模和云构建者中没有太多机会,但会在 HPC 系统的采用。

CPU 上的 AI 推理成为 CPU 设计的驱动因素,并且正在走向 V1 和 V2。N2 核心可能会被 5G 和其他网络角色以及 DPU 所采用。但其中一些市场将被2021早期的E系列所蚕食。

在 E 系列中,从 N 系列中移除了部分 5G 和网络工作,Arm采用了 Cortex-A510 内核,这是 Cortex A55 的推动者,并用于从手表到各种客户端设备智能手机,并将其移至 Neoverse E 系列服务器设计以创建 E2 平台,支持与 V2 和 N2 内核和平台相同的内存和 I/O 功能,并且支持 Armv9-A 架构。具体来说,E2 平台具有 Cortex-A510 内核和与 N2 和 V2 平台相同的背板:CMN-700 网状互连、执行硬件虚拟化的 GIC-700 中断控制器和 MMU-700系统内存管理单元。

*声明:本文系原作者创作。文章内容系其个人观点,我方转载仅为分享与讨论,不代表我方赞成或认同,如有异议,请联系后台。

,免责声明:本文仅代表文章作者的个人观点,与本站无关。其原创性、真实性以及文中陈述文字和内容未经本站证实,对本文以及其中全部或者部分内容文字的真实性、完整性和原创性本站不作任何保证或承诺,请读者仅作参考,并自行核实相关内容。文章投诉邮箱:anhduc.ph@yahoo.com