3d闪存未来走向(3D闪存只讲堆叠层数不谈制程工艺的背后)

在我们打开一个固态硬盘的产品信息页面时,总是能看到"采用3D NAND闪存"这样的介绍。大家是否想过,为什么3D结构会取代制程微缩成为闪存的发展方向?

15nm制程成为2D与3D闪存的分水岭,在15nm之后闪存不再像CPU那样继续向更先进的10nm、7nm制程迈进。是什么样的原因使得更先进的半导体制程与NAND闪存无缘?现在的3D闪存到底又是什么制程节点制造的?

TLC转折点

各种闪存新技术的出现,本质上都是为了降低每GB容量的成本。NAND闪存相比内存有一个优势,它在一个单元里可以存储多个比特(bit)的数据。这是制程微缩之外的另一种扩容量、降成本手段。当发展到TLC(3bit/cell)后,遇上麻烦了。

闪存单元的FG浮栅结构就像一个可以存储电子的桶,其中容纳的电子数量会影响到闪存单元的读取阈值电压Vth。在TLC中为了表达3比特数据已经需要用到8种不同的阈值电压,如果发展到QLC的4bit/cell结构,更需要区分出16种阈值电压,这就像蝇头小楷一样难以看清。

电子危机

制程微缩的过程进一步加剧了闪存危机,新制程的FG浮栅结构中能容纳的电子总数不断下降,发展到一个非常危险的水平。下图中的红线是过去BCH纠错技术下的可用界限,除非改变闪存结构,否则制程微缩将难以为继:制造出的闪存单元会因为能够容纳的电子数量太少而极其容易出错。

3D闪存架构提出

3D闪存就是攻城狮们找到的新结构出路。早在2007年,东芝就首次提出BiCS三维闪存结构,成功地解决了当代的发展难题。目前市场上在售的固态硬盘几乎全部使用了3D闪存。

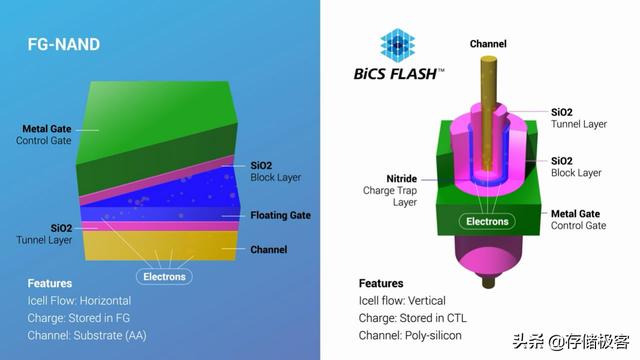

3D闪存并不是简单地把闪存单元从平面堆叠成立体状态,而是涉及了基础的结构变化。下图为东芝BiCS三维闪存与传统平面闪存的结构对比。

最终结果使得闪存单元之间的间隙变大、读写干扰得到降低。同时,Charge Trap取代了传统的Floating Gate结构,有力地提升了闪存单元"抓住"电子的能力,降低了漏电速度。

3D闪存的制程信息

很多地方说3D闪存之所以更耐用,是因为使用了更老的制造工艺。这一点其实只适用于初代的3D NAND,40nm的制程使得初代的3D闪存非常昂贵,没有达到扩容量、降成本的初衷。

尽管闪存原厂都不再透露3D闪存的具体制程信息,TechInsights的分析报告还是给出了我们想要的答案:目前的64层堆叠、96层堆叠技术使用的都是19/20 nm制造工艺。

3D闪存的未来

现在3D闪存已经在固态硬盘当中大为普及,未来还会有4D闪存吗?其实4D概念去年就有闪存厂商提出,不过"4D"只是将闪存中的外围电路拿出来,置于存储单元阵列的下方,属于3D工艺的一个小改进。

目前的主流3D闪存拥有64层堆叠层数,东芝在去年率先宣布96层3D TLC。在即将到来的下个节点是96层堆叠与QLC的结合,东芝的96层BiCS4已实现1.33Tb/die的存储密度,如果以8die封装来计算,每个闪存颗粒就可以提供高达1.33TB的海量存储空间,手机和固态硬盘的容量即将迎来又一次爆发式增长。

免责声明:本文仅代表文章作者的个人观点,与本站无关。其原创性、真实性以及文中陈述文字和内容未经本站证实,对本文以及其中全部或者部分内容文字的真实性、完整性和原创性本站不作任何保证或承诺,请读者仅作参考,并自行核实相关内容。文章投诉邮箱:anhduc.ph@yahoo.com